# **OPEN ACCESS INTERNATIONAL JOURNAL OF SCIENCE & ENGINEERING**

# SIMULATION AND ANALYSIS OF TEMPERATURE EFFECT ON 7 nm n-MOSFET

Gayatri Gaikwad<sup>1</sup>, Milan Sasmal<sup>2</sup>, Sudhir Lande<sup>3</sup>

Department of Electronics and Telecommunication, Vidyapratishthan Kamalnayan Bajaj Institute of Engineering and Technology, Baramati, India.<sup>1,2,3</sup>

gayatri.gaikwad@vpkbiet.org<sup>1</sup>, milan.sasmal@vpkbiet.org<sup>2</sup>, sudhir.lande@vpkbiet.org<sup>3</sup>

Abstract: In this paper, a detailed study has been performed to investigate the temperature effect of drain current, threshold, transconductance and sub-threshold leakage current of 7nm MOSFET. To execute this study, simulations were carried out using HSPICE simulator. Investigation of temperature effect ranging from -60 to 20°C was carried out throughout the study. The performance of MOSFET was estimated through drain current, threshold voltage, and transconductance and sub-threshold leakage current. Linear decrease in drain current and threshold voltage with increase in temperature was observed. Lowering the temperature, the current of MOSFET raises because of mobility of electrons & holes increased. HSPICE is friendly software which helps to successful process of implementation and data extraction.

Keywords: BISM, Threshold Voltage, Sub-threshold leakage current, Transconductance and HSPICE.

# I INTRODUCTION

MOSFET technology has been used in different digital and analog electronics applications. It has become a backbone of semiconductor industries of modern electronics [1].Carrier mobility of NMOS and PMOS are 1400  $cm^2/Vs$  and 450cm<sup>2</sup>/Vs respectively [2].Carrier mobility of NMOS is higher than PMOS, therefore NMOS is used for high speed since as compared to PMOS. While as compared the cross sectional area NMOS is smaller than PMOS.As junction area is smaller and drain current is higher than PMOS, so the NMOS perform faster than PMOS [3].MOS high performance technology can be deal with power dissipation for complex integrated circuit such as microprocessor. But for low operating power technology with high performance applications, then we have to reduce the power consumption of operating circuit. To reduce the power consumption by decrementing the supply voltage as low as possible [4].

To deal with the power consumption with higher performance, scaling of MOSFET technology is essential [5]. As scaling down the MOS technology continually improving the performance as more and more devices packed in smaller area of chip. So scaling is attractive due to electrical compatibility with existing circuit. So, when during a scaling, trade off among the performance and compatibility of existing technology, reliability, complexity and device performance, scaling technology has been providing a very essential technology for microelectronics.

At the early stage in 1971, 10µm channel length MOSFET has been used, then after 1997, 250nm MOSFET have been served to electronics. As speed improvement is 20% and area decremented by 30% per year [7], though from 250 nm to 7 nm technologies, there are largest change in performance, area of circuits, cost and power per function. As finFET technology has been introduced in nanotechnology, but there is a poor short channel control [8].

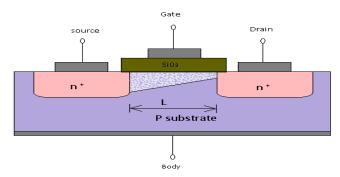

MOSFET technologies have superior scalability, improved transport properties and CMOS compatibility. The schematic of nMOSFET is shown in Figure1

Figure 1 Model structure of N type MOSFET

While doing a scaling, density of circuit is increased due to that raise in temperature. Hence, it is very important to understand the effect of temperature on device while scaling down technology [9].For low power consumption with high density packages on chip, we have to reduce a supply voltage [10], but are some limitations in scaling down a voltage. However scaling technology served a crucial technique to reduce a supply voltage with high package density. Drain current is mainly dependent on supply voltage, however scaling down the technology it is very urge to find out effect of temperature on drain current [11]. From the literature, we can say that drain current is affected by temperature with scaling down technology [12].

To reinforce the performance of MOSFET without miniaturization, we can use a low temperature technique [13]. This is useful for no. of application like aerospace application, satellite applications, high-sensitivity cooled sensor, terrestrial space mission and low noise receiver [14]. These are applications for a different low temperature to study the performance of device. Due to reduction in temperature there are some parameters which are affected like threshold voltage, drain current, transconductance and sub-threshold leakage current [15] - [19].

Here we have used BSIM4 model of 7nm MOSFET for simulation. To study effect of temperature on 7nm MOSFET, PTM file of 7nm MOSFET is used to simulate using a HSPICE 2008.3 simulator. This was gives an idea about the performance of 7nm device over low temperature. Study the temperature dependent parameters is very important while lowering the temperature. Drain current with temperature dependent is change by the variation in the threshold voltage, mobility and saturation velocity [14]. Drain current is mainly dependent on supply voltage, thereby the drain current is less dependent on temperature while scaling [15].There is excess scattering as temperature increases which causes the higher in effective resistance [16]. Hence drain current decrease with temperature increases.

It is very crucial to study the effect of low temperature on performance of 7 nm MOSFET device. Here from the equation we can say effect of low temperature ranging from -60°C to 20°C on carrier channel, mobility is high, therefore it directly affects to the drain current. Mobility raised at lowering temperature due to less scattering. Drain current of MOSFET is derived using some basic [17].

$$I_{d} = \mu C_{ox} \frac{w (v_{gs} - v_{ds})^{2}}{2L}$$

(1)

The above equation can be used to represent the MOSFET model. In this equation,  $C_{OX}$  is the capacitance of the oxide layer.  $\mu$  is the charge-carrier effective mobility, L is channel length.

While studying of temperature dependence characteristics of MOSFET, The threshold voltage is very important parameter. Drain current of MOSFET is proportional to threshold voltage and gate voltage therefore any small variation causes a larger change in drain current ( $I_d$ ). Thus the temperature dependent study of threshold voltage is very important and many parameters are associated to the threshold voltage while studying the temperature dependent characteristics MOSFET [18]-[19].

$$\frac{\delta V_{th}}{\delta T} = \frac{\delta \Phi_F}{\delta T} \left[ \alpha \sqrt{\frac{q \epsilon_{si} N_{eff}}{\Phi_F C_{ox}^2} + 2 + \frac{q D_{it}}{C_{ox}}} \right] \quad (2)$$

Where  $\mathcal{C}_{si}$  and q are the silicon permittivity and electron charge;  $\alpha = 1$  for partially depleted devices and  $\alpha = 0$  for fully depleted transistors. Eq. (2) increases when the temperature decreases [20].

Sub threshold leakage current is also an important temperature dependent parameter. When transistor is in OFF mode, there is current flow in between source to drain current called sub-threshold leakage current. The Sub-Threshold is term from gate voltage  $V_{gs}$  is smaller than threshold voltage. It is very important to find out the power dissipation of device [21]-[22].An accurate estimation of the sub-threshold behavior by means of physical modeling is important for the device and circuit [23]. The following equation shows the sub-threshold leakage current of MOSFET which is denoted by  $I_{Sub}$  [24].

$$I_{sub} = \frac{\mu W_{eff} c_{ox}}{L_{eff}} V_T^2 e^{(|V_{GS}| - |V_t|)} / \eta V_T \left( 1 - e^{-|V_{DS}|} / V_T \right)$$

(3)

Where  $W_{eff}$  is Effective transistor width and  $L_{eff}$  is Effective channel length,  $\eta$  is Sub-threshold swing coefficient and  $V_T$  is Thermal voltage.

Analysis of transconductance  $G_m$  in linear and saturation low temperatures using analytical expressions for gm derived by using simple square law MOSFET current model [25]-[27].

$$G_m = \frac{\beta(T)v_{ds}}{2} \tag{4}$$

#### **II.RESULT AND DISCUSSIONS**

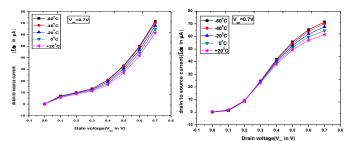

We pay particular attention to the low temperature and electric field. Figure 2 (a) and (b) shows the currentvoltage characteristics of MOSFET at different temperature. To verify the model of MOSFET, the I-V characteristics of MOSFET with different temperature has shown. Temperature effect on current-voltage gives an idea about the performance of device while variation in temperature. Figure 2 (a) and (b) shows simulated drain current of MOSFET with channel length of 7 nm measure at different temperature. A simulated result of I-V Characteristics at different temperature explained temperature dependent shift in drain current. While keeping the supply voltage 0.7V, Figure 2 (a) shows the comparison of simulation of transfer I-V characteristics at different temperature. We performed for n-MOSFET at fixed  $V_{ds}$ =0.7V.In Figure 2 (b) I-V curve shows the output characteristics of same MOSFET at different temperature with keeping  $V_{as}$ =0.7V.

Figure 2 (a) Transfer characteristics with different temperature (b) Output characteristics at different temperature.

The simulated temperature dependent data obtained for low temperature range -60°C to 20°C.Here temperature increasing the drain current falls with linearly in all cases. Typically Fig.3 (a) shows drain current verses temperature with fixed  $V_{gs} = V_{ds} = 0.7$  V. The negative temperature range -60°C to 20°C the drain current changes from 71.5  $\mu$ A to 61.5  $\mu$ A respectively. From this graph, it is clear that increasing temperature cause a decrease in mobility [16]. If this decreases mobility is almost dependent of drain current. Drain current decreases constantly for various fixed values of supply voltage as temperature increases.

Threshold voltage is important parameter in study of temperature dependence of MOSFET characteristics. Change in  $V_{th}$  with temperature are shown and compared with measured data as shown in Fig.3 (b).

Figure 3: (a) Drain current variation with temperature (b) Threshold voltage variation with temperature with  $V_{gs}=V_{ds}=0.7V$

As the temperature reduced the threshold voltage increased because when temperature decreases carriers in channel become freeze. So that higher gate voltage should be provided to invert the channel [19].MOSFET has a  $V_{th}$ = 182mV at room temperature and  $V_{th}$ =209mV at -60°C.There

is large variation of threshold voltage cause in drain current of MOSFET. It has been observed that most of current change about 11% on an average is due to a threshold voltage [14].Drain and source resistance change monotonously with temperature.

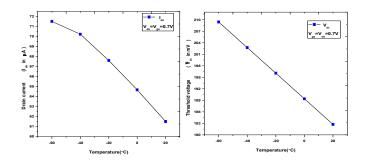

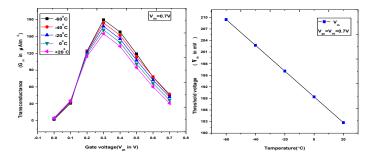

Use A transconductance at gate biases close to threshold voltage will drops gradually with temperature due to mobility degradation with temperature [26]. Characteristics for NMOS of  $W/_L = {14}/_7$  standard CMOS process at various temperatures are shown in Fig. 4 (a) and (b).In this, a  $V_{gs}$ =0.3V identified maximum variation in transcoductance. As temperature increases,  $G_m$  gradually decreases due to mobility reduction with temperature while threshold voltage reduction with temperature has negligible effect on  $G_m$  in the linear region as indicated by equation (4).

Figure 4 (a) Transconductance variation with gate voltage  $(V_{gs})$  at different temperature at  $V_{ds} = 0.7V$  (b) Transconductance (Gm) variation with temperature

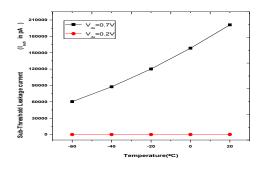

The Effect of temperature on sub-threshold leakage current is essential in digital VLSI circuits. Simulation of Sub-threshold leakage current with different temperature is shown in Fig 5.In offset state of mode the sub-threshold leakage increased linearly with increased in temperature and voltage [22]. Fig 5. Shows the variation in sub-threshold leakage current in various temperature ranging from -60°C to 20°C with  $V_{ds}$ =0.7V.

Figure 5: Sub-threshold leakage current variation with temperature at  $V_{ds}$ =0.2V and  $V_{ds}$ =0.7V

It can clearly be seen that for different  $V_{ds}$  varying from 0.7 V to 0.2V a significant reduction in sub-threshold leakage current. At  $V_{ds}$ , it rises exponentially with temperature [22]. At temperature (-60°C) and  $V_{ds} = 0.7$  V,  $I_{leak}$  is 62.491E<sup>-9</sup> A, while at temperature (20°C) and  $V_{ds} = 0.7$ V it goes up to 204.17E<sup>-9</sup> A i.e 69% change. At temperature (-60°C) and  $V_{ds} = 0.2$ V,  $I_{leak}$  is 147.58E<sup>-12</sup> A while at temperature (20°C) and  $V_{ds} = 0.2$ V it goes to 13.61E<sup>-12</sup> A i.e 91% change. So it is conclude that this change is very high. Therefore as Temperature change, the effect become prominent on leakage current.

#### **III CONCLUSION**

The work is done with focus of parameters of 7nm n-MOSFETs, which can be useful in low temperature applications. Devices showed an increasing due to the increasing the mobility of charge carriers of channel as a reduction in temperature. As the threshold voltage and mobility increased at lower temperature so we can say that drain current improved at lower temperature. It clear from graphs the threshold voltage, transcoductance and sub-threshold leakage current depending upon temperature. The graph of transconductance characteristics is an image of the variation of electron concentration in the channel with temperature. Transconductance is increase in linear region but decreases in saturation region.

## ACKNOWLEDGMENT

First author would like to thank Dr. Sudhir Lande and Dr. Milan Sasmal of VPKBIET, Baramati for support and moral encouragement given while carrying out research work for ME degree and also, support and co-operation from the department of ENTC.

#### REFERENCES

- [1] Paulo "IEEE SSCS DL Lectures at SEMINATEC 2012"

IEEE SOLID-STATE CIRCUITS MAGAZINE, April 2012.

- [2] V. Arora, M. Tan, "Quantum Nanoelectronics: Challenges and Opportunities", IEEE conference on semiconductor electronics, 2008.

- [3] M. Lundstrom, Z. Ren, S.Datta," Essential Physics of Carrier Transport in nanoscale MOSFET's", IEEE Trans. Electron Devices, Vol. 51 January,2002.

- [4] M. Manghisoni, L. Gaioni, L. Ratti, V. Re, G. Traversi, "Assessment of a Low-Power 65 nm CMOS Technology for Analog Front-End Design", IEEE TRANSACTIONS ON NUCLEAR SCIENCE, VOL. 61, NO. 1, FEBRUARY 2014.

- [5] D. CRITCHLOW "MOSFET Scaling—The Driver of VLSI Technology", PROCEEDINGS OF THE IEEE, VOL. 87, NO. 4, APRIL 1999.

- [6] M. Kumar, "Effects of Scaling on MOS Device Performance" IOSR Journal of VLSI and Signal Processing (IOSR-JVSP) Vol. 5, Issue 1, PP 25-28 e-ISSN: 2319 – 4200, p-ISSN No. : 2319 – 4197, Jan - Feb. 2015.

- [7] D. Critchlow, "Recollections on MOSFET Scaling", IEEE SSCS NEWSLETTER 2012.

- [8] Y. Nara, "Scaling Challenges of MOSFET for 32nm Node and Beyond" International Symposium on VLSI Technology, Systems, and Applications, 2009.

- [9] Ja Chun Ku and I. Yehea, "On the Scaling of Temperature-Dependent Effects" IEEE TRANSACTIONS ON COMPUTER-AIDED DESIGN OF INTEGRATED CIRCUITS AND SYSTEMS, VOL. 26, NO. 10, OCTOBER 2007.

- [10] W. Fikry, G. Ghibaudo, M. Dutoit, "Temperature Dependence of Drain Induced Barrier Lowering in Deep Sub-micrometer MOSFETs," Electronics Letters, vol. 30, no. 11, pp. 911-912, 1994.

- [11]S. Mohapatra, K. Pradhan, P. Sahu, "Investigation of Dimension Effects of FD-S-SOIMOSFET in Nanoscale", 1st International Conference on Emerging Technology Trends in Electronics, Communication and Networking, 2012.

- [12] R. Das, S. Maity, D. Muchahary, C. Bhunia, "Temperature dependent study of Fin-FET drain current through optimization of controlling gate parameters and dielectric material", Super lattices and Microstructures, January 2017.

- [13] S. Kalra, "Effect of temperature dependence on performance of Digital CMOS circuit technologies" INTERNATIONAL CONFERENCE ON SIGNAL PROCESSING AND COMMUNICATION (ICSC), 392 – 395, 2013.

- [14] N. Sachdeva, N. Julka, "Effect of Temperature Fluctuations on MOSFET Characteristics", International Journal of Electronics & Communication Technology, I S SN: 2230 - 7109, Vol. 2, Issue 1, March 2011.

- [15] J. Singh, G. Wadhwa, "MOSFET Mobility Model at Nanoscale Including Temperature Effects", 3rd International Conference on Computer Research and Development, Vol.3, no. 325 – 330, 2011.

- [16] S. Vemulapati, U. Traub, "Packaging SiC power semiconductors-Challenges, technologies and strategies", in Wide Bandgap Power Devices and Applications (WiPDA), IEEE workshop, Vol. 18, no. 23, pp.13-15, oct.2014.

- [17] S. Jahdi, O. Alatise, P. Alexakis, Li Ran, P. Mawby, "The Impact of Temperature and Switching Rate on the Dynamic Characteristics of Silicon Carbide Schottky Barrier Diodes and MOSFETs" IEEE TRANSACTIONS

ON INDUSTRIAL ELECTRONICS, VOL. 62, NO. 1, JANUARY 2015.

- [18] R. Wang, J. Dunkley, T. De Massa, L. Jelsma, "Threshold Voltage Variations with Temperature in MOS Transistors," IEEE Electron Device Letters, vol. 18, no. 6, pp. 386-388, 1971.

- [19] I. M. Filanovsky, A. Allam, "Mutual Compensation of Mobility and Threshold Voltage Temperature Effects with Applications in CMOS Circuits," IEEE Transactions on Circuits and Systems I: Fundamental Theory and Applications, vol. 48, no. 7, pp. 876-884, 2001.

- [20] M. Gupta, A. Kranti "Variation of Threshold Voltage With Temperature in Impact Ionization-Induced Steep Switching Si and Ge Junctionless MOSFETs" IEEE TRANSACTIONS ON ELECTRON DEVICES March 4, 2017.

- [21] A. Kayalvizhi, "Analysis of leakage current calculation for nanoscale MOSFET and FinFET", international journal for trends in engineering& technology vol. 4, April 2015.

- [22] M. Bhuyan, F. Ferdous, Q. Khosru, "Temperature Effects on Sub-threshold current of Pocket Implanted Nano Scale n-MOSFET", 7th international conference on electrical and computer engineering, December 2012.

- [23] N. Shukla, S. Birla, K. Rathi, R. Singh, M. Pattanaik, "Analysis of Effect of temperature and Vdd on Leakage current in conventional 6T-SRAM Bit-Cell at 90 nm and 65 nm Technology", International Journal of Computer Applications (0975 – 8887) Volume 26– No.1, July2011.

- [24] R. Singh, P. Bhatnagar, Geetanjali, D. Sahu, N. Shukla, A. Goel, "Analysis of the Effect of Temperature Variations on Sub-threshold Leakage Current in P3 and P4SRAM Cells at Deep Sub-micron..." International Journal of Computer Applications (0975 – 8887) Volume 35– No.5, December 2011.

- [25] A. Osman, M. Osman "Investigation of High Temperature Effects on MOSFET Transconductance", Fourth International High Temperature Electronics Conference. HITEC (Cat. No.98EX145), pp301 – 304, 1998.

- [26] J. Colinge, "Transconductance of Silicon-on-Insulator (SOI) MOSFETs" IEEE electron device letters, vol. edl-6 no. 11, November 1985.

- [27] P. Toledo, H. Klimach, D. Cordova, S. Bampi, E. Fabris, "CMOS Transconductance Analysis for Low temperature sensitivity Based on ZTC MOSFET condition"2015.

## BIOGRAPHY

**Gayatri Gaikwad** received BE degree from PICT college of Engineering, Pune. Currently she is pursuing her M.E. degree upon in electronics (Digital Systems) from Vidyapratisthan Kamalnayan Bajaj Institute of Engineering and Technology, under Savitri Bai Phule Pune University.

**Milan Sasmal** received the Bachelors (Hons.) degree from Vidyasagar University, Paschim Medinipur, India, and M.Sc. degree from Jadavpur University, Kolkata, India, in 2001 and 2003, respectively both in Electronic Science. He received M.Tech. degree in Materials Engineering from the

Bengal Engineering and Science University, Shibpur, India, in 2008. He obtained Ph.D. degree, Indian Institute of Technology Kharagpur, Kharagpur, India. He is an Assistant Professor of Electronics and Telecommunication Engineering department, Vidyapratisthan Kamalnayan Bajaj Institute of Engineering and Technology. His current research interests. **Sudhir Lande** received the Bachelors (Hons.) degree from

B.E. (Electronics Engineering.), from KITS, Ramtek, Nagpur University in 1996 and M. Tech. in Telecommunication System Engineering (TSE) from IIT, Kharagpur in 2002. He has been awarded Ph.D. on "Resource Allocation and Management in OFDMA with CSI and QoS for Next generation wireless Network" by RTM

Nagpur University in 2014.